Sony schließt sich FDSOI Verein, EE Times

MADISON, Wis -. Sony Corp. ergab, dass die nächste Generation Global Navigation Satellite System (GNSS) Chip des Unternehmens 28-nm Fully Depleted Silicon On Insulator (FDSOI) Verfahren verwendet wird.

Das japanische Unternehmen verwendet STMicroelectronics 28nm FDSOI Design-Kit, und hergestellt seine FDSOI Proben bei ST fab.

Während Anhalten kurz einen Starttermin für den Chip von der Ankündigung teilte das japanische Unternehmen auf dem Forum seine eigene FDSOI „Design-Erfahrung,“ es ist ein Daumen nach oben geben. Der Sprecher Kenichi Nakano von Sony gab einen Vortrag mit dem Titel „Low Power SoC-Design mit HF-Schaltung durch die FDSOI 28nm.“

Ein STMicroelectronics Vertreter sagte EE Times, „FDSOI ist nicht mehr nur eine ST-Geschichte mehr.“ Wenn das SOI-Forum ist jede Maßnahme, das FDSOI Ökosystem zusammen kommen. Andere Moderatoren enthalten Samsung, VeriSilicon, Open Silicon, Synopsys und Cadence. Sie berichteten, ihre eigenen Ergebnisse und IP mit FDSOI.

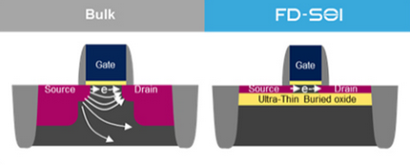

FD-SOI-Transistors ermöglicht eine bessere elektrostatische Eigenschaften im Vergleich zu herkömmlichen bulk-Technologie. Die vergrabene Oxidschicht reduziert die parasitäre Kapazität zwischen der Source und dem Drain.

Um den Stromverbrauch für die GNSS-Chips geschnitten, setzte Nakano aus hat alles von RF, Logik und SRAM auf dem Chip bei 0,6 V betrieben wird, anstelle von 1,1V.

Nakano Team versucht, die 28-nm-FDSOI Prozess aus, testeten die Design Machbarkeit und bestätigt, dass es alle Leistungsziele unter Verwendung von Test-Elementgruppe (TEG) Auswertung erreichen können.

VeriSilicon Senior Director of Engineering, Shirley Jin, der sagte, ihr Unternehmen verfügt über einen umfangreichen IP-Portfolio in 28-nm-FDSOI, der Arbeits Design-Flow und Infrastruktur, um die Entwürfe auszuführen, resümierten VeriSilicon Design Erfahrung in ihrer Präsentation.

Der Aufruf FDSOI „eine energieeffiziente Technologie“, sagte Jin, „28nm FDSOI Aktien die meisten die gleichen Geräte wie Bulk-Prozess und ermöglicht eine einfache Konstruktion zu portieren.“ Die 28-nm-FDSOI ermöglicht ein flexibles Design Trade-off für Energie / Leistung und bietet gute Nutzung der Körper-bias-Techniken. Zum Beispiel, nach vorne Körper Bias (FBB) kann die Leistung weiter verbessern, während umgeKörper Bias (RBB) Leckage reduzieren.

Das ist mein 2-cts auf diesen langen Faden.

User-Rang

Autor

Sang Kim, Sie jetzt diese gleichen Beitrag mehrfach gemacht haben, und haben bereits zu jeder Zeit genau geantwortet worden zeigt, wo Ihre Behauptungen sind wriong (ITRS Skalierung, SOI Dicke usw.). Wenn Sie die Antworten nicht verstehen kann, hat es keinen Sinn dieses Themas fort.

User-Rang

Autor

FDSOI ist nicht skalierbar. Wie ultradünnen SOI-Dicke ist erforderlich

für 14nm FDSOI? Weniger als 4 nm. 4 nm gilt als sein

Ende der Skalierung nach RTRS weil 3 nm, 2 nm, 1 nm

stattdessen unterliegen strukturellen quantenmechanischen Confinement-Effekte sind nicht mehr Gegenstand der klassischen Physik Gerät,

in Erhöhung der Vt führt, eine große Variation der elektrischen Übertragungs

Eigenschaften wie Vt, subthreshold Steigung, did / DVG,

dId / DVD. etc. Oder unterliegen Unsicherheit.

Könnten Sie meine fünf falschen „Fakten“ weisen darauf hin, nach Ihrem

Konto, damit ich antworten kann?

User-Rang

Autor

Samsungs Präsentationen zeigen, dass 28FDSOI bessere Leistung - vor allem eine niedrigere Leistung - und ähnliche oder geringere Kosten pro Chip als 28nm Bulk, wenn Sie dies nicht glauben, dann fragen Sie sich, warum sie all die Anstrengungen der Erziehung eines solchen Verfahrens gehen ? Wie viele Male gesagt worden ist, wird die erhöhte Waferkosten durch einfachere Verarbeitung (weniger Masken / Stufen) kompensiert, und es wird die Verarbeitung, wo die meisten der Waferkosten geht.

Die Tatsache, dass 14nm FDSOI ist noch nicht in der Produktion nicht zeigt es nicht skalierbar ist, zeigt es nur, dass es im Vergleich zu FinFET verzögert wird - als 28nm FDSOI bis 28nm Bulk-Vergleich war. Wie AKH0 Sie hält zu sagen, die SOI-Ausgangsdicke> 10 nm und diese perfekt herstellbar ist und seit einigen Jahren, fertig SOI Dicke selbst für den 10 nm-Knoten 5 nm und das ist auch in Ordnung. Ihre Zahlen sind einfach falsch, die Gate-Längen sind nicht das gleiche wie der „Prozessknoten“ (wie ist sehr gut bekannt), und die SOI-Dicken sind viel kleiner als die Realität.

Die Leute halten Sie sagen, über das Thema zu gehen und zu lesen, weil Sie die gleiche falsche „Fakten“ (zum Beispiel über Gatelänge, Substratdicke, Herstellbarkeit, Skalierung, Kosten) halten über die Entsendung immer und immer wieder; selbst dann, wenn es darauf ist, dass Ihre „Fakten“ sind falsch und wo die richtig diejenigen zu finden, umbuchen Sie immer noch die gleich, die wieder (mindestens fünfmal jetzt nach meiner Zählung). Dies ist keine Sache Meinung oder Debatte, Ihre sogenannten „Fakten“ sind einfach falsch.

User-Rang

Autor

28nm bulk plane Transistoren Volumen hergestellt für

einige Jahre von den großen Halbleiter-Unternehmen wie

wie Intel, TSMC, Samsung, GF und andere, aber 28nm SOI oder

FDSOI Technologie-basierte Geräte sind noch nicht hergestellt

von den großen Halbleiter-Unternehmen. Können Sie mir sagen

Warum? Es sei denn, 28nm FDSOI zeigt eine bessere Leistung und

hat weniger Herstellungskosten im Vergleich zu 28-nm-Bulk,

28nm FDSOI wird nicht wegen eines SOI-Wafer hergestellt werden

allein Kosten 4 oder 5 mal höher ist als eine Normal Wafer und

möglicherweise auch höhere Verarbeitungskosten. Es scheint, die Debatte

Ich habe nicht die anti-FDSOI / pro-FinFET Fragen. Vielmehr würde ich

gerne 28nm FDSOI / 28nm Bulk-Hobel Probleme haben, weil

22nm und 14nm FinFET sind in Massenproduktion über zwei

Jahre von Intel und 16nm FinFET in diesem Jahr hergestellt von

TSMC aber FDSOI nicht auf 22nm, 16nm gefertigt und

14nm Knoten noch. So zeigt es FDSOI ist nicht skalierbar Gegenteil

zu FinFET weil etwa 5 nm, 4 nm und etwa 3 nm SOI

Dicken für 22nm, 16nm und 14nm erforderlich FDSOI

Geräte sind nicht herstellbare. 4 nm gilt als sein

Ende der Skalierung nach ITRS.

Wie ich bereits sagte, ist dies kein Forum mir zu sagen, wer

sollte meinen Lehrer oder Ihren Lehrer und welche Papiere sein

und Bücher zu lesen oder die Wörter wie „endlos FUD“ zu verwenden.

Dies ist nicht das erste Mal. Habe ich mich jemals so in

hier beide Ansichten auf FDSOI. Ich mag Zuschauer hören

Meinungen zu FDSOI Technologie. Das ist alles.

User-Rang

Autor

„Nehmen wir nun an, die (Löcher) von der Quelle gesammelt als

im Gegensatz zu gesammelt durch die gut in der Masse MOSFET, Was

geschadet wird?“Der Schaden angerichtet ist groß Leckstrom

kommt aus dem in Durchlaßrichtung vorgespannten N + (Quelle) P (Löcher)

Diode wie Loch induzierte Barriere wie DIBL Absenken

Verschlechtern der MOSFET Leistung, sogar zum Ausfall.

Intels erste 22nm finFET wurde entwickelt und

hergestellt, um Leckstrom zu unterdrücken. 28nm oder

30nm ist bulk Hobel nicht FinFET. Die Rippenstrukturen

einschließlich fin hoch, Flossenbreite an der Unterseite und Gate-

Länge von 22-nm-FinFET Intel wurden durch TEM bestimmt

Querschnitt nicht nur von Intel und anderen konformen t

er Gatelänge gleich 22 nm, 30 nm nicht. Ich weiß nicht recht

verstehen, warum TSMC 16nm Anruf finFET statt

30nm FinFET. 30nm gehört zum Bulk-Hobel, nicht

Wieder einmal würde Ich mag von ganzem Herzen hören, Ihre

technische Sichtweisen einschließlich Meinungsverschiedenheiten, aber

ehrlich gesagt nicht gerne hören, Ihre rät wie was

Papiere zu lesen, wie lange soll ich lesen, die

Konferenzen ich teilnehmen soll. etc. Das ist nicht Ihr

spätestens eine gerade hier gepostet.